# ANDANTE

### UC 1.2: Colour Classification at the Edge for Quality Control

## Overview & Setup

- Quality control is an important part of the production process of every kind of product

- Sensor and AI become more and more important for quality control but have latency, confidentiality and scalability issues

- IFAG and EESY explore the neuromorphic technology, analog NNs, for extreme edge application to manage these issues

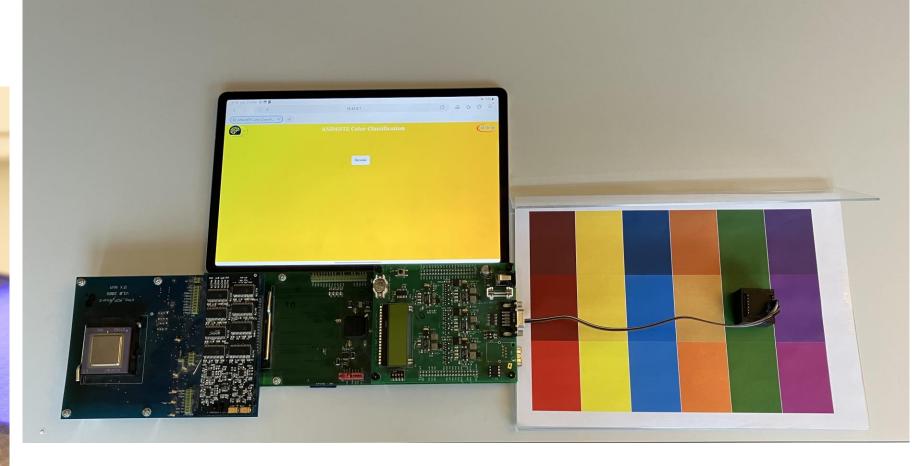

- Demonstrator setup consist of:

- Board 4.1 with ASIC3.2

- 1 color sensor, color board, tablet and Raspberry Pi

- Processing pipeline with small analogue NN models

## Technology

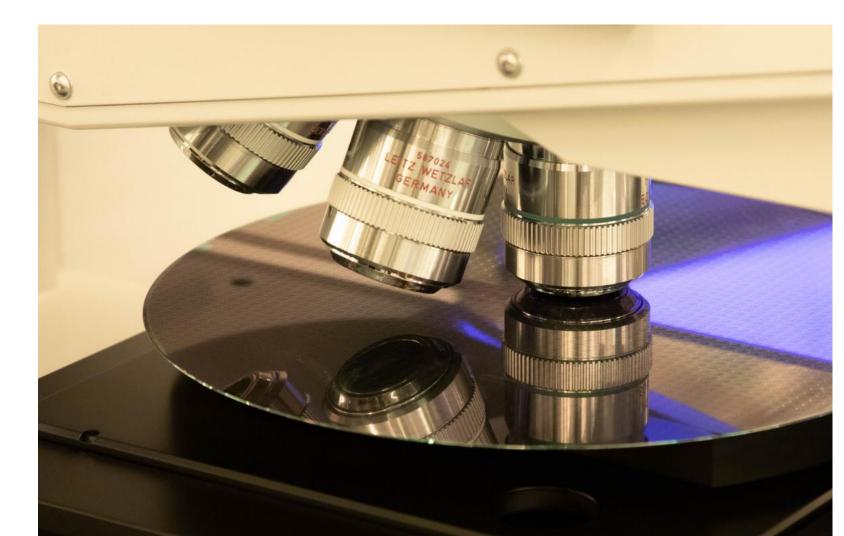

- ASIC 3.2 is based on 28 HPC+ technology with a RRAM memory array at its core

It has a static model architecture with adaptable

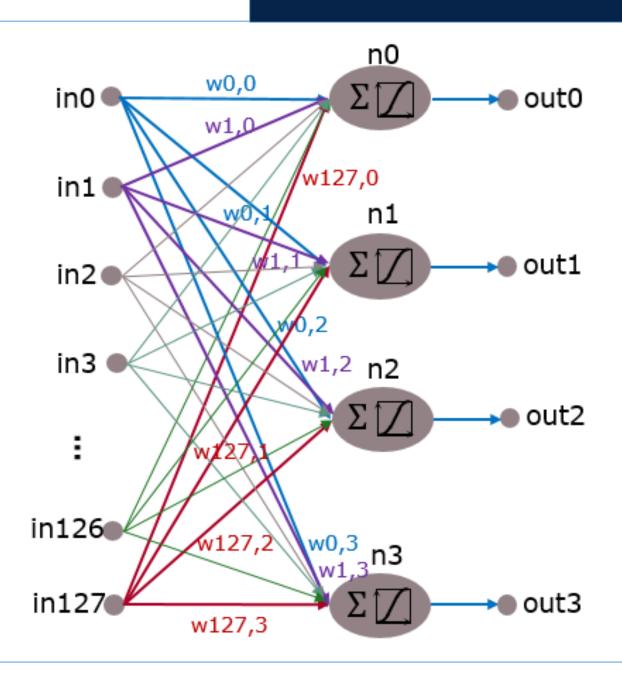

- It has a static model architecture with adaptable weights

- The architecture consists of 128 input neurons, 4 hidden and output neurons distributed over 3 layers

- Board 4.1 is based on an existing test bench from IFAG

- During ANDANTE IFAG focused on the improvement of components for evaluation e.g. the software for the programable voltage board

### Results

- Two types of data sets were gathered with the color board:

- Simple variant consist of yellow, blue, green and orange

- Complex variant containing all color on the board

- Evaluation showed:

- Targets could not be reached due to:

- "Empty space" on the chip

- Static network architecture

- However, simple variant is not far off

- Most likely the range of possible application is limited as the accuracy of the complex variant indicates

#### Impact

- Feasibility of the selected approaches for simple applications was proven

- Moving towards commercialization by:

- Improving model approach and hardware concepts

- Optimize ASIC implementation and transfer to smaller technology nodes

- Focusing on optimizing algorithms and hardware for a specific set of applications e.g. key word spotting

- Looking into efficient integration of the concepts into sensor node circuits

# Progress beyond SoA

- One of the first moves towards implementing AI at the extreme edge (directly in/at the sensor)

- Researching RRAM memory in the context of analog NN and extreme edge applications

- Concepts for miniaturization of AI and compressing functionality with AI for smaller devices

#### Lessons learned

- Further improvements of algorithms and hardware concepts for the extreme edge required

- Trade-off between flexibility regarding possible applications and resource limitation is challenging

- Upper limits regarding possible usage of developed concepts need to be investigated

ANDANTE

AI for New Devices And Technologies at the Edge

🛱 andante-ai.edu

in linkedin.com/company/andante-ai

Scan Me to visit website