#### 🗾 Fraunhofer IPMS

### Overview

- Fraunhofer IPMS is exploring FeFET based Compute-In-memory accelerators

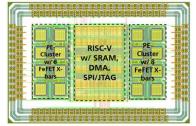

- . For the exploration Fraunhofer IPMS developed the mixed-signal neural network ASIC 3.1b based on 28SLPe + technology with a FeFET memory array at its core

- Accelerator connected RISC-V coprocessor via DMA for flexibility •

- An adapter board was developed to characterize the chip on wafer-level

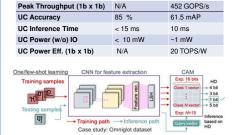

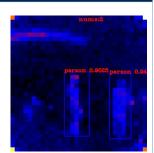

- UC1.1: People Counting using infrared thermopile arrays to detect radiation pattern of persons

Segment structure

scalability

Simulated

# FeFET Compute-In-Memory

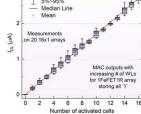

- FeFET based 1F1R concept implemented in low-mismatch, lowleakage segment structure

- MAC operation by Kirchhoff's law of current accumulation

- Passive array programming schemes implemented

- Pattern structures to be loaded

- Retention >10<sup>8</sup> s and endurance >10<sup>5</sup> tested

- ASIC 3.1b: ANN ASIC for the extreme edge

- Integrated with a RISC-V for adaptability and controllability

- Mapping of various networks supported

- Flexible quantization of weights and activations

KPI Name

8nm FeFET Crossbar Based Analog Ir Memory Computing Accelerator

Results

Target

Memory augmented neural network (MANN) few-shot learning reference case

# Impact

- Feasibility of concepts proved

- Next steps for commercialization: Optimize ASIC implementation and

- transfer to smaller technology nodes Looking into efficient integration of the

- concepts into sensor node circuits

#### ANDANTE

🛱 andante-ai.edu

applications

# Lessons learned

- Trade-off between flexibility regarding possible applications and resource limitation is challenging

- HW-SW co-design necessary for high performing designs

#### AI for New Devices And Technologies at the Edge

g 30

20 10

in linkedin.com/company/andante-ai

ECSEL Joint Undertaking

"This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement N $_{

m e}$ 876925. The JU receives support from the European Union's Horizon 2020 research and innovation programme and France, Belgium, Germany, Netherlands, Portugal, Spain and Switzerland"

Scan Me to visit website

mAF Validated MAC outputs 25%~75%

3-way,

- 3-sho

Progress beyond SoA

One of the first moves towards using

FeFET for compute-in-memory

Researching FeFET memory in the

context of analogue NN and tinyML

Largest array demonstration

#### I/O interfaces: SPI, UART, I2C, I2S Weight Memory: FeFET Instruction Memory: SRAM Accelerator controlled with custom DMA module Hierarchical accelerator design for